cache : 자주 쓰이는 데이터를 저장하며, 매우 빠른 Access time 을 지원하는 컴퓨터 메모리이다.

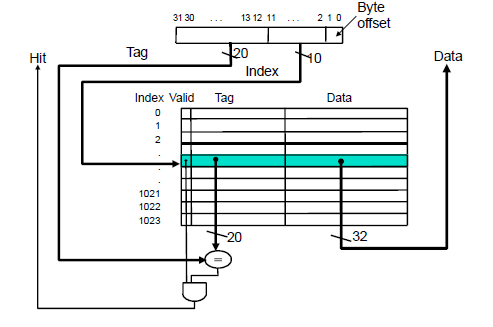

기본적 캐시 구조

- direct mapped : cache와 main memory 간에 mapping 이 되어있는 것 , cache를 통해 main memory data를 가져와야 한다

▶ 캐시에서의 위치 : main memory 주소 % 캐시 block의 개수

예시) main memory : 22번지 캐시 block : 8개 ☞ 캐시에서의 위치 : 6 (=22%8)

▶ 하지만 이 방법은 main memory의 여러 주소가 한 곳의 캐시에 들어가게 되는데, 캐시에서 그 값이 main memory 중 어디를 가르키는지 알려면 어떻게 해야할까?

답) 유효비트(valid bit)와 tag를 이용한다.

앞의 2bit (00,01,10,11)로 main memory 중 어디인지 구분, 유효비트가 1이어야 접근하기 유효한 주소이다.

- 20 bit : tag 구분을 위해

- 10 bit : 2^10 개의 cache block의 Index를 위해

- 2 bit : 4 byte offset을 위해 (00,01,10,11) -> 1word = 4byte 이고 메모리의 용량을 1024word라고 결정하면 그 안에서 4byte를 구분해주는 요소가 필요 , 그게바로 2bit

ex) cache = 1024 words , 1word = 4byte

offset = 2 bit, index = 10bit, tag = 20 bit

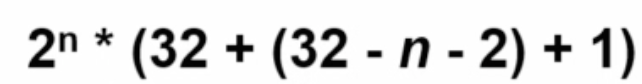

cache 용량 = (32bit (데이터) + 20bit(tag) + 1bit(valid) *1024)

blocksize가 1 word (=4 bytes) 일 때,

식이 성립한다.

HIT & MISS

Read Hits : 읽으려는 데이터가 캐시에 있다.

Read Miss : 읽으려는 데이터가 캐시에 없다. (CPU 정지 -> memory로 부터 block을 가져옴 -> 캐시로 block 전달 -> CPU 재시작)

■ CPU 정지 = memory로 부터 데이터를 받아오기를 기다리며 내부의 모든 레지스터를 동결

■ separate controller가 캐시 miss에 대한 행동을 수행한다. (메인 메모리로부터 데이터 fetch, 메모리를 캐시에 넣음)

■ 데이터 저장 후, CPU 재실행

Handling cache miss

이전에, instruction memory와 data memory를 나눴었다. 따라서 캐시도 instruction 캐시와, data 캐시로 나눈다.

Read miss 일 때,

[instruction cache] - write 동작 없음 ( memory에 새로운 데이터를 입력하기만 하면 된다.)

1.PC - 4를 해서 돌아간다.

2. CPU stall, 메모리로부터 block을 받는다.

3.cache에 block을 입력, valid bit = 1

4. instruction execution 재실행

[data cache] - 읽기, 쓰기 둘다함

cache하고 memory하고 내용이 일치를 안할 수도 있다.

miss 가 나서 새로 data를 저장하게 되는데, 이때 옛날 값(old block)을 어떻게 해야할까?

답) write policy 에 따라 다르다.(옛날값 저장 or 그냥 버림)

write policy

▶ write through : cache의 block과 main memory의 block을 동시에 update

- miss일 때, old block 걍 버림

- 고로, miss일 때 속도가 빠름

- 오히려 hit 일 때, cache와 main memory 모두 update해야해서 시간이 더 걸림, memory에 계속 접근함

☞ 메모리 접근이 적다는 캐시의 장점이 없어진다.

▶ write back : cache만 update, main memory에서 데이터를 갖다쓸 일이 새기면, 바뀐 cache값을 main memory에 저장

- Dirty : Dirty bit = 1

cache block에 새로운 데이터가 write되었을 때 (main 에는 old block 유지)

main 에서 메모리를 갖다쓸일이 생기면 write back을 한다.

- Clean : Dirty Bit = 0

cache block이 업데이트 되지 않은 상황

write back 필요 없음

-> cache의 크기는 조금 늘어나지만, memory access가 줄어드는 방식

Write

Write through는 write buffer를 이용한다. 왜냐하면 cache와 main memory를 같이쓰는데, memory 접근은 속도가 굉장히 느리기 때문에 buffer에 write할 데이터를 쌓아놓는다.

-processor : 데이터를 cache와 buffer에 write

-memory controller : buffer의 데이터를 main memory(DRAM)으로 전송

Read Hit : 우리가 원하는 것이 cache에 있다.

Read miss : 우리가 원하는 것이 cache에 없다.

miss 가 난 번지만 업데이트하는 것이 아니고, 1 block을 다 업데이트 해야한다. (1 block은 1word, 2word 등 다양할 수 있다.)

data는 block단위로 이동한다(spatial locality)

miss penalty 는 위치를 탐색하는 시간 + read하는 시간 + cache에서 다른 메모리 쫒아내는 데 걸리는 시간

=> memory read + memory write하는 시간

64KB = 2의 16승 , address = 16bit

cache의 한 block의 크기 8 byte = > 구분하려면 3bit 필요

cache entry : 2의 8승 (8bit 필요)

byte offset = 3bit

index = 8bit

tag = 16 - 8 - 3

data의 크기는? 1 block의 크기가 8byte니까 64bit

1byte 는 8 bit

valid가 0 이면 태그가 맞아도 못쓰는 주소임

'ੈ✩‧₊˚Computer Science > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조]캐시 메모리 성능 향상 (improving cache memory performance) / three placement policy (1) | 2020.11.26 |

|---|---|

| [컴퓨터구조] 부동 소수점 연산(Floating point number arithmetic) (0) | 2020.11.22 |

| [컴퓨터구조] 메모리 계층구조 기본 (Memory hierarchy general) (0) | 2020.11.20 |

| [컴퓨터구조]Data hazard (forwarding) (0) | 2020.11.17 |

| [컴퓨터구조] Pipelining Hazard (파이프라인 해저드) (0) | 2020.11.13 |